cs61c_lab5

Part 1: Sub-Circuits

NAND1

NOR1

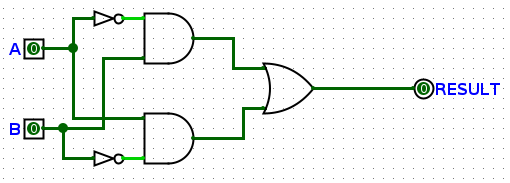

XOR1

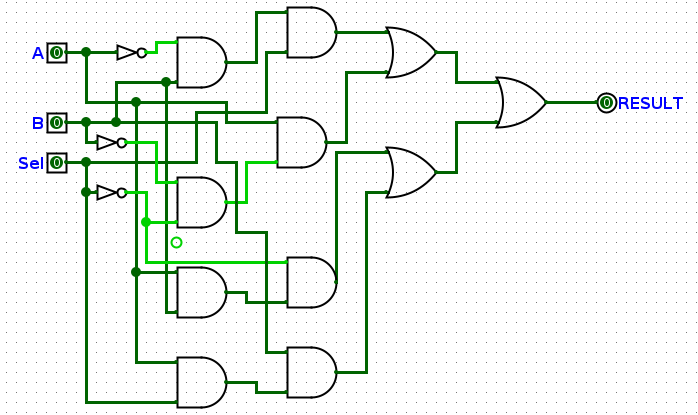

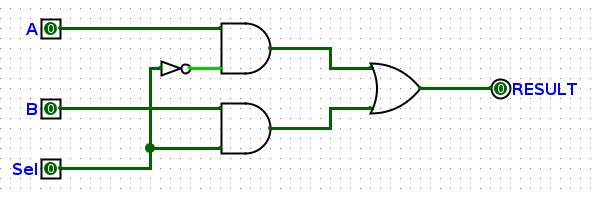

MUX2

通过列真值表可以得到以下逻辑式:

\(\neg{A}BSel+A\neg{B}\neg{Sel}+AB\neg{Sel}+ABSel=RESULT\)

可以画出如下电路:

参考大佬的电路图后发现可以化简1: \[ RESULT=\neg{A}BSel+A\neg{B}\neg{Sel}+AB\neg{Sel}+ABSel \\=BSel(A+\neg{A})+A\neg{Sel}(B+\neg{B})\\=A\neg{Sel}+BSel \] 化简后电路图如下:

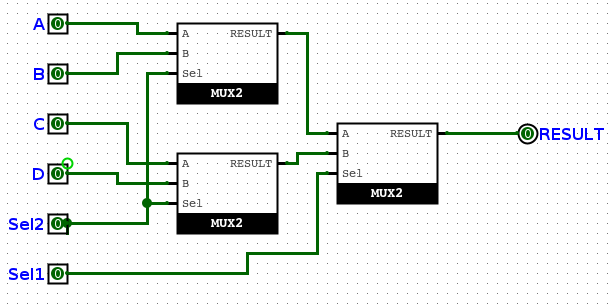

MUX4

两个MUX2可以组成一个MUX4

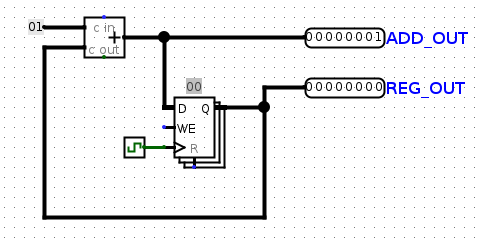

Part 2: Storing State

Part 3: FSMs to Digital Logic

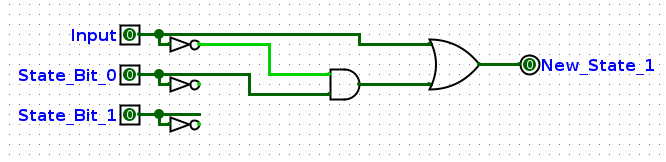

StateBitOne

根据真值表化简后可得 \[

st1_{next} = input + st0\neg{input}

\]

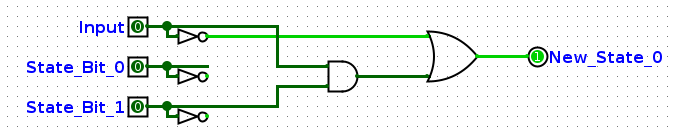

StateBitZero

根据真值表化简后可得 \[

st0_{next} = \neg{input} + st1\dot{input}

\]

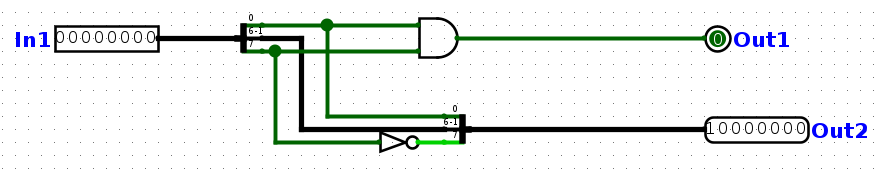

Part 4: Practice with Splitters

如下:

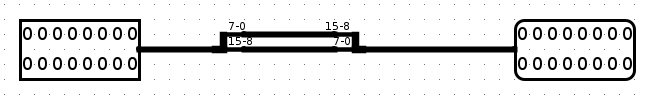

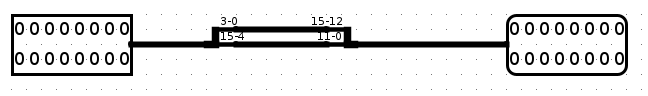

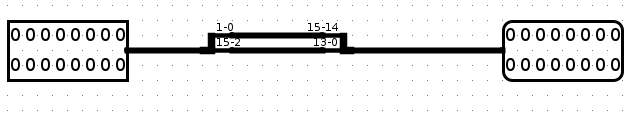

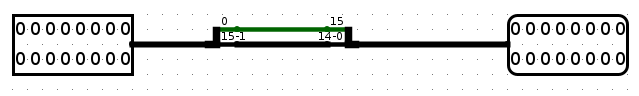

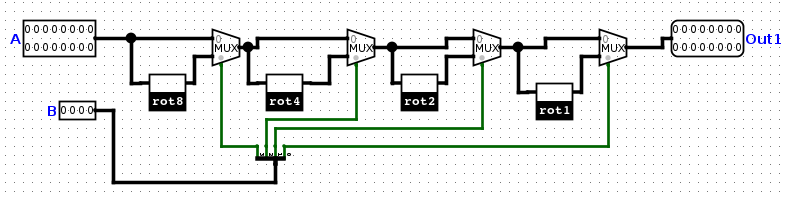

Part 5: Rotate Right

rot8

rot4

rot2

rot1

rotr

https:/github.com/PKUFlyingPig/CS61C-labs/blob/master/lab05_Logism/ex1.circ↩︎